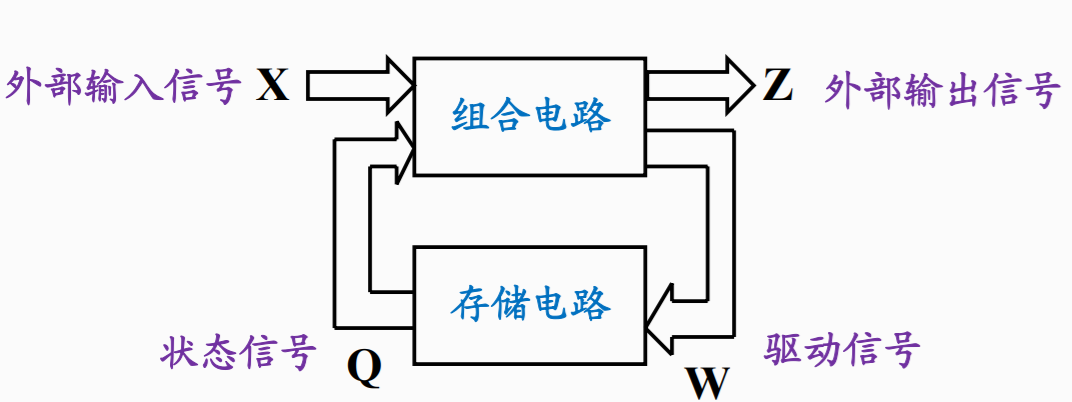

时序逻辑电路

电路在任何时候的输出稳定值,不仅与该时刻的输入信号有关,而且与该时刻以前的电路状态有关;电路结构具有反馈回路

解决了:

- 自动运行的问题。时序电路接通之后可以不停地开启和关闭开关,进入一个自动运行的状态

- 存储的问题。通过时序电路实现的触发器,能把计算结果存储在特定的电路里面

- 解决了各个功能按照时序协调的问题,使得不同的事件按照时间顺序发生

存储电路

存储电路由存储器件组成,能存储一位二值信号的存储器件称为存储单元电路。存储单元电路大多是双稳态电路

- 锁存器

- 触发器

分类

按存储电路中存储单元状态改变的特点分类

- 同步时序电路

- 异步时序电路

按输出信号的特点分类

米里(Mealy)型: 输出信号不仅仅取决于存储电路的状态,而且还取决于外部输入信号

摩尔(Moore)型: 输出信号仅仅取决于存储电路的状态,而和该时刻的外部输入信号无关

按逻辑功能分类

- 计数器

- 寄存器

- 移位寄存器

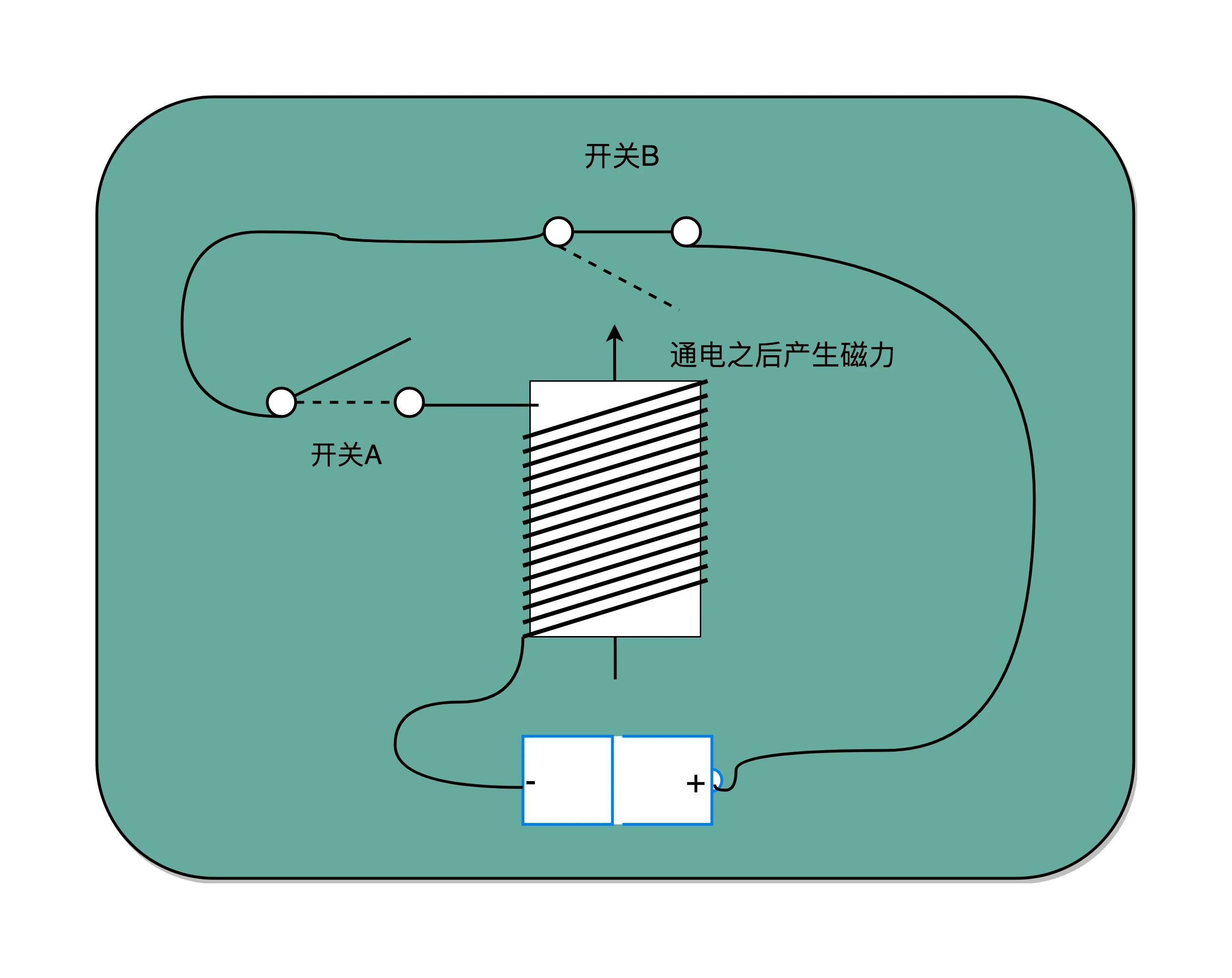

时钟硬件

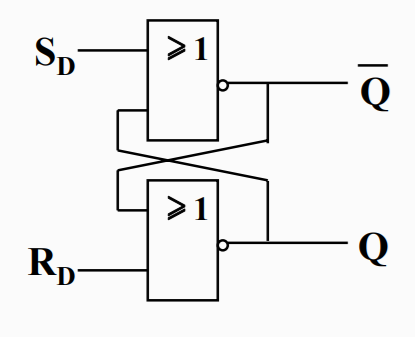

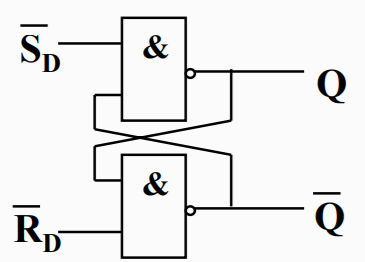

RS锁存器

- 或非门构造的锁存器

- 与非门

- SD —置位端(置1端)

- RD —复位端(置0端)

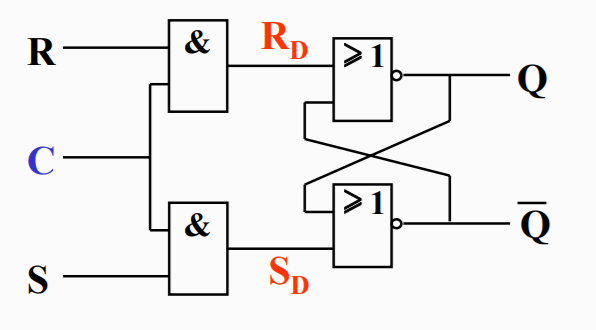

门控锁存器

- 当C=1时: 门控RS锁存器功能和RS锁存器完全相同

- 当C=0时: RD=SD=0,锁存器状态保持不变

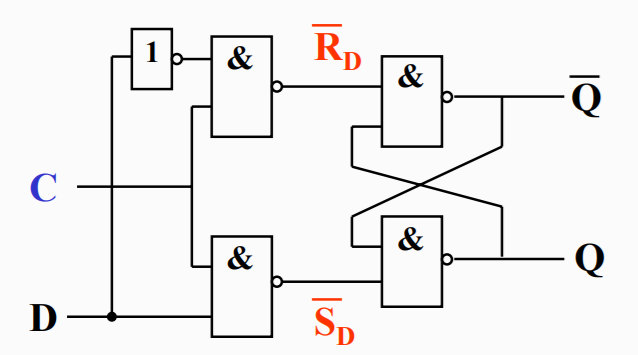

门控 D 锁存器

- 当C=0时,RD=SD=1,电路处于保持状态;

- 当C=1时,RD=D, SD=D,电路的新状态为D

触发器

利用“时钟”的特殊定时控制信号去限制存储单元状态的改变时间,具有这种特点的存储单元电路称为触发器(FF:Flip-Flop)

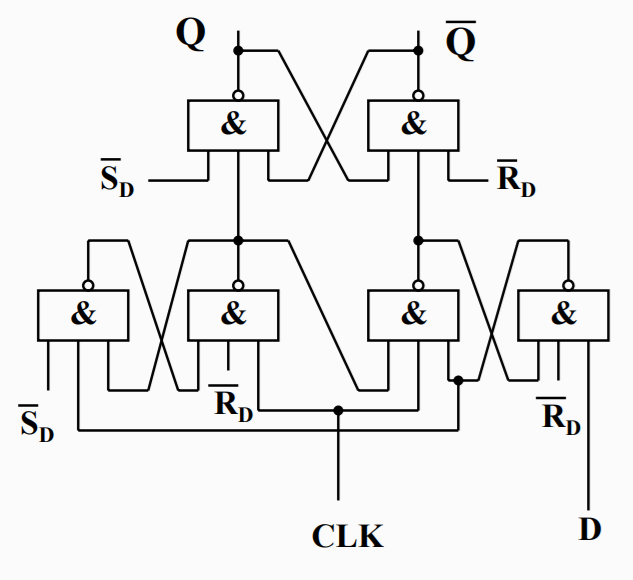

边沿D触发器

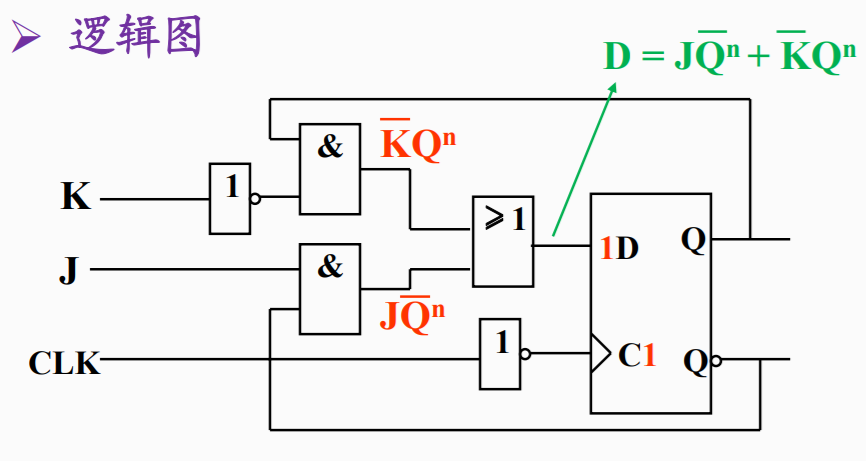

负边沿JK触发器

触发器脉冲工作特性

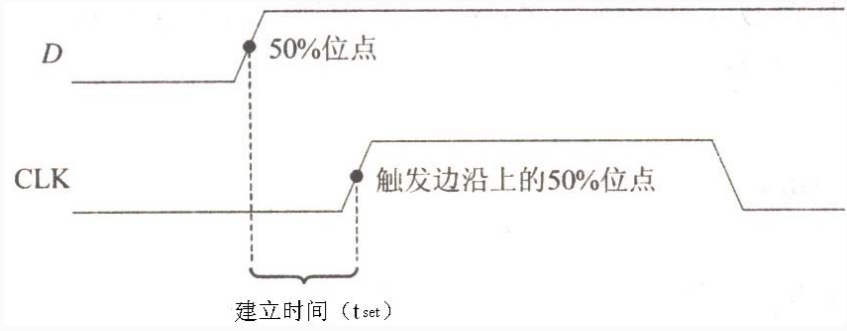

- 建立时间

为使触发器做好触发准备,要求输入信号在时钟脉冲的边沿到来之前,提前一段时间到来,提前的这段时间叫建立时间,用tset表示。

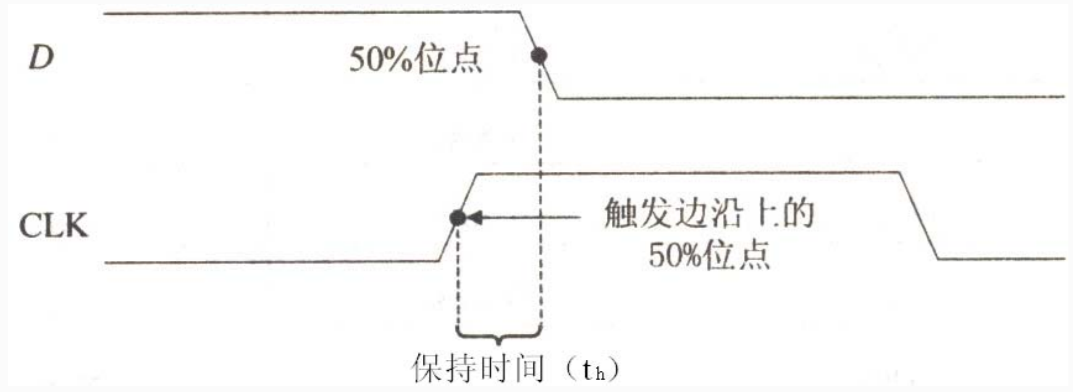

- 保持时间

为了保证触发器可靠翻转,在时钟脉冲到达后,输入信号必须维持一段时间不变。这段时间称为保持时间,用th表示

- 传输延迟时间

从时钟脉冲边沿到触发器的新状态稳定建立起来,所需要的时间叫做传输延迟时间

- 最高时钟频率

在保证触发器可靠翻转的条件下, 所允许的时钟频率有一个上限值 (最高频率) ,该上限值即为触发器的最高时钟频率,用fmax表示

锁存器应用

- 消颤开关

触发器应用

- 单脉冲发生器

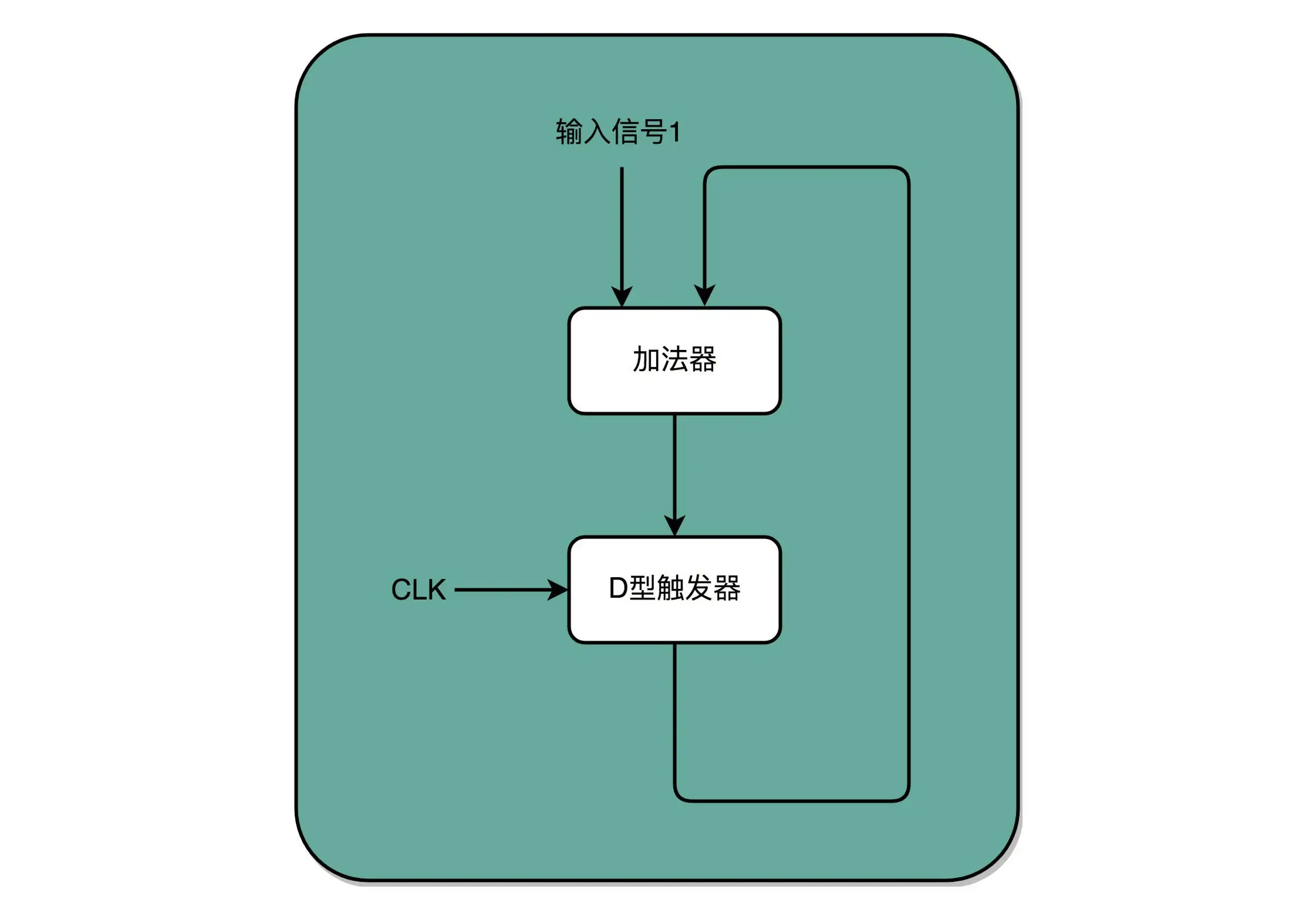

PC寄存器实现

同步时序电路

分析

只要知道了在当前状态下各触发器的输入(即驱动信号),就能根据触发器的特性方程,求得电路的下一个状态,最终找到电路的状态转换规律

设计

- 根据逻辑功能要求,建立原始状态表或原始状态图;

- 利用状态化简技术,简化原始状态表,消去多余状态;

- 状态分配或状态编码,即将简化后的状态用二进制 代码表示;

- 选择触发器类型,并根据编码后的状态表求出驱动方程和输出方程;

- 检查自启动性, 若所设计电路中存在无效状态, 则必须检查电路能否自启动, 如果不能自启动, 则需修改设计;

- 画出逻辑图。